SRAMメモリへの『読み』『書き』の動作

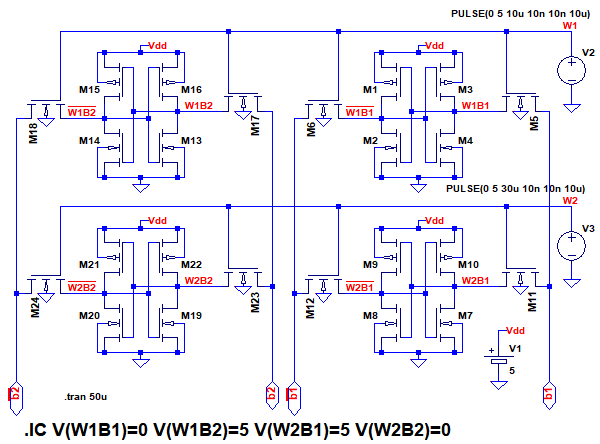

図1は,4つのSRAMメモリ・セルの読み出し動作をシミュレーションする回路図です.データ幅を2ビット,データ数を2ワードに簡略化して読み出しのシミュレーションを行います.シミュレーション開始,10μs後にワード線(W1)へ,30μs後にワード線(W2)へ,振幅5Vでパルス幅10μsの信号を加えます.この条件で,50μsのトランジェント解析を行います.

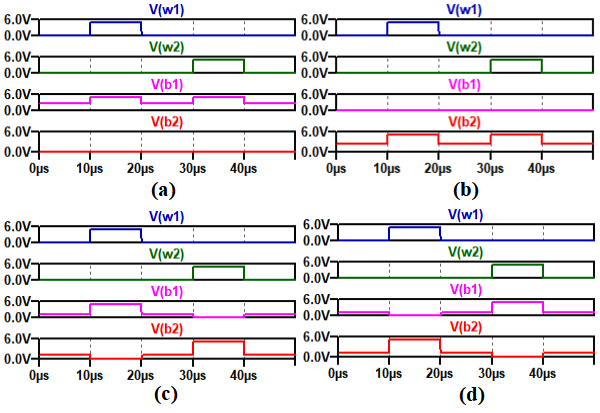

図2は,図1のワード線W1とW2,ビット線b1とb2のシミュレーション結果です.W1,W2,b1,b2の信号の関係として正しいのは,図2の(a)~(d)のどれでしょうか.なお,回路の初期値は「.ICコマンド」で決まるものとします.

ワード線W1とW2にパルスを入力したときの,ビット線b1とb2の波形は?

W1,W2,b1,b2の信号の関係として正しいのは?

(a)の結果 (b)の結果 (c)の結果 (d)の結果

SRAM(Static Random Access Memory)は,マイコンなどのメモリとして使用されます.6個のトランジスタで1つのメモリ・セルを構成しています.データを読み出す場合,ワード線でメモリ・セルの位置を指定し,ビット線にデータが出力されます.通常は8ビット単位でデータを読み出しますが,図1では2ビットに簡略化されています.「.ICコマンド」で各メモリ・セルがどのように初期化されるかを考えれば答えは簡単にわかります.

図1の回路の初期値は「.ICコマンド」で決まります.つまり内部のメモリ・セルの記憶状態は「.IC」の内容で決定されることになります.「.IC V(W1B1)=0 V(W1B2)=5 V(W2B1)=5 V(W2B2)=0」となっているため,W1B1が0V,W1B2が5V,W2B1が5V,W2B2が0Vになります.

W1がHigh("H")レベルのとき,b1に,W1B1の値が出力され0Vとなり,b2に,W1B2の値が出力され5Vとなります.次に,W2が"H"レベルのとき,b1にW2B1の値が出力され5Vとなり,b2にW2B2の値が出力され0Vとなります.このようになっていのは(d)なので,正解は(d)の結果となります.

●SRAMのメモリ・セルの構造

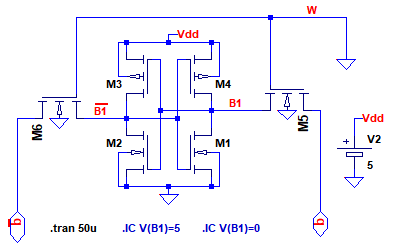

図3は,図1のSRAMメモリ・セルを1つだけ取り出したものです.6個のMOSトランジスタで構成されています.M1とM4,M2とM3で,それぞれインバータを構成し,互いの出力と入力が接続されています.M5とM6は,指定したデータを取り出すためのスイッチとして働きます.bとbの2つを取り出すのは,差動信号として取り出すことで,ノイズによる誤動作を低減するためです.

なお,LTspiceでは,ノード名の前に"_"をつけて"_b"とすると,回路図上では文字に上線が付き,"b"と表示されます.

6個のMOSトランジスタで構成されている.

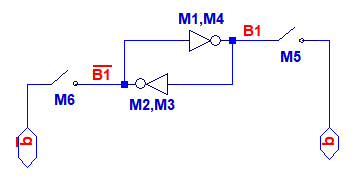

図4は,図3の回路をインバータの記号を使用して書き換えたものです.B1が1の場合,B1は0となり,安定します.また,B1が0の場合B1は1となり,この状態でも安定します.このように2つの状態を保持できるため,記憶素子として使用することができます.

2つの状態を保持できるため,記憶素子として使用できる.

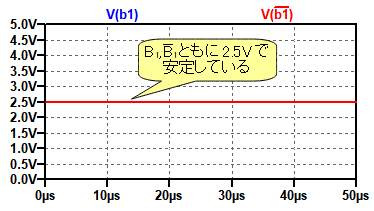

図5は図3の回路のシミュレーション結果です.B1,B1ともに2.5Vで安定しています.回路シミュレータでは素子間に特性のバラツキがないため,中間電圧で安定してしまうことがあります.このような場合,「.ICコマンド」を使用することで初期値を設定することができます.

B1,B1ともに2.5Vで安定している

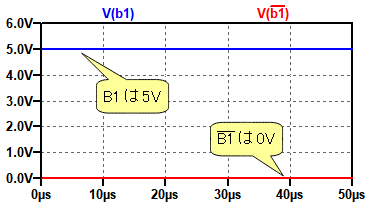

図6は「.IC V(B1)=5」というコマンドを追加してシミュレーションした結果です.B1が5V,B1が0Vで安定しています.ICコマンドは,回路の動作点が複数あるために,シミュレーション結果が収束せずにエラーとなっていまう場合の対策としても有効です.

B1が5V,B1が0Vで安定している.

●SRAMのメモリ『読み出し動作』をシミュレーションする

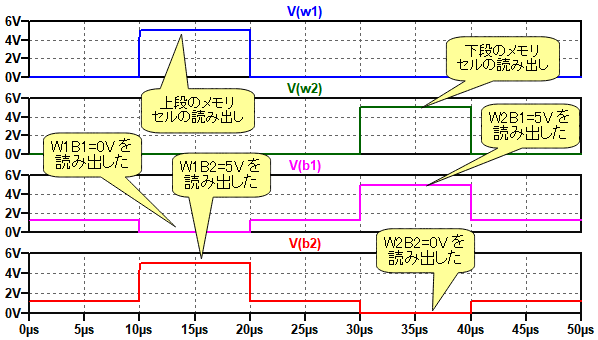

図7は図1のSRAMの読み出し動作のシミュレーション結果です.

W1が5Vのときに上段のメモリ・セルを読み出し,W2が5Vのときに下段のメモリ・セルを読み出す.

W1端子が5Vになると,M5とM17がオンし,b1端子にはW1B1端子の0Vが出力され,b2端子にはW1B2端子の5Vが出力されます.次にW2端子が5Vになると,M11とM23がオンし,b1端子にはW2B1端子の5Vが出力され,b2端子にはW2B2端子の0Vが出力されます.これは,図2の(d)と同じものです.

●SRAMのメモリ『書き込み動作』をシミュレーションする

図8がSRAMの書き込み動作をシミュレーションするための回路です.b1,b1,b2,b2にデータ用の信号を加えて,W1,W2の信号でメモリ・セルに書き込みます.

b1,b1,b2,b2にデータ用の信号を加えて,W1,W2の信号でメモリ・セルに書き込む

M5,M6など,スイッチ用のMOSFETは駆動能力を大きくするため,L=1uというパラメータを追加しています.LTspiceのMOSFETのディフォルトのL,Wは100μとなっているため,Lを1μとすることで,駆動能力を100倍とすることができます.スイッチ用MOSFETの駆動能力を大きくすることで,メモリ・セルの状態を強制的に変更できるようになります.「.IC」による初期化は「.IC V(W1B1)=0 V(W1B2)=0 V(W2B1)=0 V(W2B2)=0」とすべて0Vとなるようにしてあります.

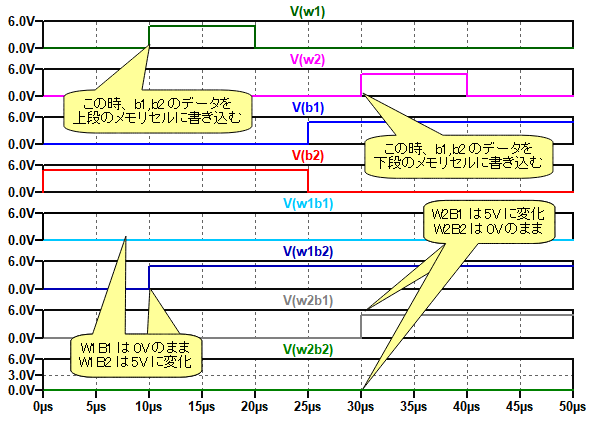

図9が図8のシミュレーション結果です.

W1,W2が"H"レベルになるタイミングでb1,b2のデータが書き込まれている.

W1が"H"レベルになるタイミングでは,b1が0V,b2が5Vとなっているため,W1B1は0Vのままで,W1B2は5Vに変化しています.次にW2が"H"レベルになるタイミングでは,b1が5V,b2が0Vとなっているため,W2B1は5Vに変化し,W1B2は0Vのままとなっています.このようにSRAMにデータが書き込めることが分かります.

以上,SRAMの構成と動作の基本について解説しました.実際のSRAM ICでは,高速に動作させるため,回路やタイミングなど,さまざまな工夫が追加されています.

解説に使用しました,LTspiceの回路をダウンロードできます.

LTspice7_043.zip

●データ・ファイル内容

SRAM.asc:図3の回路

SRAM_2B2W.asc:図1の回路

SRAM_2B2W.plt:図7のグラフを描画するためのPlot settinngsファイル

SRAM_2B2W_write.asc:図8の回路

SRAM_2B2W_write.plt:図9のグラフを描画するためのPlot settinngsファイル

■LTspice関連リンク先

(01) LTspice ダウンロード先

(02) LTspice Users Club

(03) トランジスタ技術公式サイト LTspiceの部屋はこちら

(04) LTspice メール・マガジン全アーカイブs

(05) ◆LTspice電子回路マラソン・アーカイブs

(06) ◆LTspiceアナログ電子回路入門アーカイブs

(07) ◆LTspice電源&アナログ回路入門アーカイブs

(08) ◆IoT時代のLTspiceアナログ回路入門アーカイブs

(09) ◆オームの法則から学ぶLTspiceアナログ回路入門アーカイブs

(10) ◆LTspiceエデュケーショナル・ファイルで学ぶアナログ回路アーカイブs